## Fabrication Suspended High-Aspect-Ratio Parylene Structures for Large Displacement Requirements

### Wen-Cheng Kuo\* and Chen-Wei Chen

Department of Mechanical and Automation Engineering, National Kaohsiung First University of Science and Technology, Taiwan (Received 15 October 2013; Accepted 10 December 2013; Published on line 1 June 2014)

\*Corresponding author: rkuo@nkfust.edu.tw

DOI: 10.5875/ausmt.v4i2.343

**Abstract:** A new method is presented for the fabrication of suspended parylene structures, using dry etching at low temperatures with a single standard silicon wafer. A silicon micro trench is used as a mold, in which parylene beams are fabricated through the deposition and removal of parylene in multiple stages, after which the structure is released from the same side of the silicon wafer. Compared to traditional processes, this approach eliminates the deposition of unnecessary silicon-dioxide, overcomes the need for double-sided micro-machining and supports the wafer during the release of the structure, thereby reducing process complexity and production costs. The proposed process is used to fabricate a test device of free-standing parylene beams 20 *um* in width, 3000 *um* in span, and 50 *um* in thickness to verify the feasibility of the structure based on suspended parylene. The ductile characteristics of the parylene beams allows elastic deformation of up to 100 *um*. CoventorWare simulation results show that parylene generates only 2.3% of the maximum Von Mises stress compared to a silicon based test device with the same dimensions. This new process is well-suited for applications to devices with large in-plane displacement and low stiffness.

Keywords: Parylene; suspended structures; MEMS

#### I. Introduction

Suspended structures are widely used as transducers in Micro-Electro-Mechanical Systems (MEMS). Soft beams with limited stiffness in the in-plane direction are required to provide a high degree of Traditional MEMS sensitivity. devices such accelerometers [1, 2] and optical switches [3, 4] are produced with single crystal silicon (SCS); however, the large Young's modulus (~150GPa) of this material prevents the creation of soft beams. One alternative approach to producing softer beams is the use of softer materials.

Polymer MEMSs have attracted a great deal of attention in recent years for sensing, actuating, and providing structure in a wide range of applications, including physical transduction, chemical analysis, and medical care [5]. The ease of fabrication at low

temperatures combined with unique mechanical flexibility makes polymeric devices a promising alternative to silicon-based devices.

Among the variety of polymer materials available, parylene (poly-para-xylylene) has been most broadly used thanks to its high flexibility (Young's Modulus ~4.7GPa [6]), ductility with large linear-elastic range (yield strain ~3 %), 30% lower TCE than SU-8 [7] or polyimide, chemical inertness, and bio-compatibility. Parvlene compatible with microfabrication technologies is suitable for deposition using pinhole-free conformal chemical vapor deposition (CVD) coating at room-temperature, and can be dry-etched using oxygen plasma [6]. These features provide parylene processes with a high degree of compatibility in conventional microfabrication techniques. Parylene MEMS technology has been under development for nearly ten years. Of the three most common parylenes (Figure 1), parylene C is most commonly used in industry.

$$\left(\begin{array}{cccc} CH_{2} & CH_{2} \end{array}\right)_{n} & \left(\begin{array}{cccc} CH_{2} & CH_{2} \end{array}\right)_{n} & \left(\begin{array}{cccc} CH_{2} & CH_{2} \end{array}\right)_{n} \\ & CH_{2} & CH_{2} \end{array}\right)_{n} & \left(\begin{array}{cccc} CH_{2} & CH_{2} \end{array}\right)_{n} \\ & Parylene N & Parylene C & Parylene D \\ & Parylene D & Parylene D \\ & Parylene$$

Figure 1. Schematic of chemical structures for the three most commonly employed parylenes.

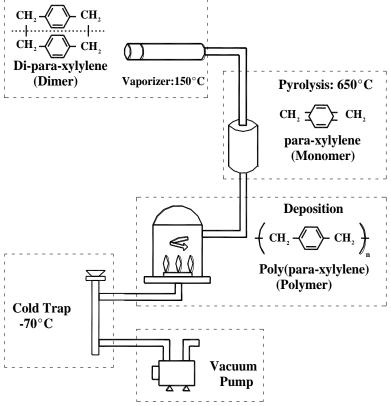

Figure 2. Schematic of parylene deposition process.

The process of parylene deposition [8] is illustrated in Figure 2. The parylene coater used in this work is adapted from the Deree Technologies Company. Parylene is deposited at room temperature at pressures of approximately 0.1 torr, with the mean free path of the molecules on the order of 0.1 cm. The first step in the deposition process is the vaporization of the solid

Wen-Cheng Kuo received his PhD in Mechanical Engineering from National Taiwan University (NTU) in 2006. He did postdoctoral work in micro-electromechanical systems (MEMS) at NTU from 2006 to 2007 followed by additional research at the Caltech Micromachining Laboratory from 2007 to 2008. He currently serves as Assistant Professor of Mechanical and Automation at National Kaohsiung First University of Science and Technology in Kaohsiung, Taiwan. His research interests focus on MEMS, including the analysis, design and fabrication of micro/nano structures, and implantable wireless bio-medical devices.

Chen-Wei Chen received the M.S. degree in Mechanical and Automation Engineering from National Kaohsiung First University of Science and Technology, Kaohsiung, Taiwan in 2011. Currently, he is the production engineer at Siliconware Precision Industries Co., Ltd. in Taichung, Taiwan. His research interests are IC dicing and package in the semiconductor industry.

dimmer by heating to 150  $\,^{\circ}\mathrm{C}$  . The second step is the pyrolysis of the dimmer, cleaving at the two methylene-methylene bonds to yield stable monomeric radicals, para-xylyene at approximately 650  $^{\circ}C$ . The monomers are driven by a pumping system into the deposition chamber at room temperature, where they polymerize on the substrate. Finally, a cold trap at approximately -70 °C is used to collect the un-reacted monomers before they enter the pumping system.

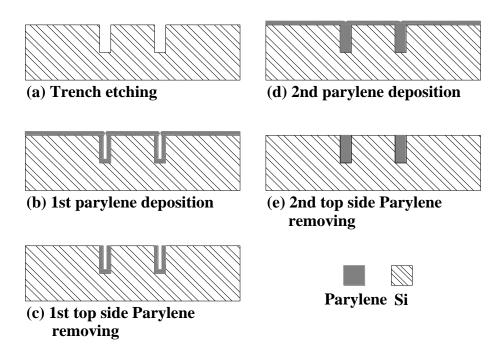

Traditionally, parylene has been deposited as a coating in thin film materials. Suzuki et al. proposed the use of a silicon micro trench as a mold, in which parylene beams produced through multi-stage [9], deposition-removal thereby extending application of parylene by providing it with a high-aspect-ratio structure. Figure 3 shows the process of fabricating the parylene beams. Figure 3 (a) shows the etching of the silicon trench to create a micro mold for the deposition of parylene. In Figure 3 (b), due to step coverage effect during the deposition of parylene, the thickness in the corners of the trench is greater than that along the sidewall, increasing the likelihood of sealing the trench in a single run through the deposition of thick parylene layers. To prevent the sealing of the trench, oxygen plasma is applied to remove the uppermost parylene, thereby re-opening the trench, as shown in Figure 3 (c). After re-opening the trench, the second

parylene layer is applied to fill the trench without voids, as shown in Figure 3 (d). The number of times that parylene must be deposited and removed is determined by the width of the trench. The creation of a larger parylene beam requires an increased number of repetitions to deposit and trim the parylene. Figure 3 (e) shows the process of removing the topmost section of parylene for the second time.

Figure 3. Schematic of method for fabricating parylene beams.

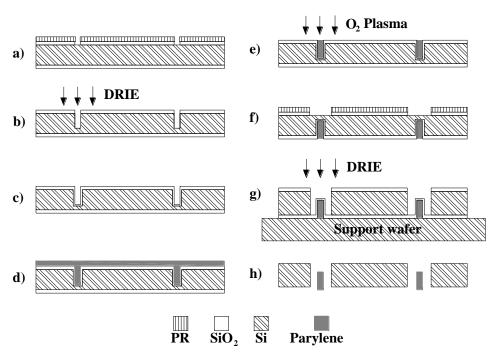

Figure 4. Traditional process flow for suspended parylene structures.

The traditional method for releasing the parylene structures [9] is illustrated in Figure 4, in which a double-sided silicon wafer is used as a substrate. This process uses patterned oxide as a mask for etching the trench. Following the creation of the trenches, a second course of oxidation is applied to the substrate to form an etch-stop layer ( $SiO_2$ ) for the etching of later trenches. This is followed by multiple steps to deposit and remove the parylene, thus creating beams in the trenches. The substrate is then placed upside down to pattern the backside oxide as a mask. To allow for the etching and releasing of the wafer through the trench, the substrate is glued to the support wafer, and the substrate is etched away from the backside to expose the parylene beams, which are covered by etch-stop ( $SiO_3$ ). Finally, the parylene beams are released by stripping off the SiO, with a buffered HF solution. This process requires high temperature oxidation, double-sided micro-machining, and a support wafer.

The parylene beams can also be released [6] using SOI wafer, where the parylene beams are released by stripping off the buried SiO<sub>2</sub> layer with a buffered HF solution. While the fabrication method is simple and straightforward, the cost of the wafer is much greater than that of single-crystal-silicon (SCS) wafer.

This paper proposes a simpler method for creating suspended parylene structures. Our process employs a single-sided polished silicon wafer as a substrate, and photoresist as an etching mask, and releases the parylene beams from the front side. This eliminates the creation of excessive thermal dioxide, overcomes the need for double-sided micro-machining and supports the wafer during the release of the structures, thereby reducing process complexity and production costs. Without the need for high temperature oxidation, the process can be performed within a low temperature environment, thereby eliminating the need to remove thermal oxide using buffered HF solution.

The remainder of this paper is organized as follows: the proposed process for fabricating suspended parylene structures is described in Section 2. Section 3 introduces a test device to create suspended parvlene structures. Test results and measurements are presented in Section 4, and conclusions are presented in Section 5.

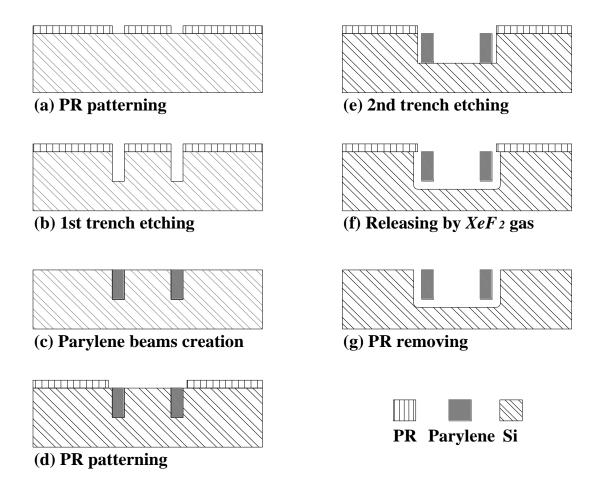

Figure 5. Proposed process flow for parylene structures: Step (a), photoresist patterning; Step (b), 1st trench etching; Step (c), fabrication of parylene beams; Step (d), photoresist patterning; Step (e), 2nd trench etching; Step (f), releasing structure; Step (g), photoresit removal.

# II. Process flow for suspended parylene structures

The proposed process uses one single-sided polished silicon wafer as a substrate, with photoresist as an etching mask, thus thermal oxide is not required. The process is illustrated in Figure 5. In the first step, photoresist is spun on a silicon wafer as an etching mask for deep silicon etching, followed by a pattern transfer process. In step (b), inductively coupled plasma (ICP) etching is used to etch the silicon to a desired depth [10, 11]. The parylene is deposited in the trenches and trimmed repeatedly to create beams in the deep trenches in step (c). In step (d), photoresist is spun on the silicon wafer as an etching mask, followed by a pattern transfer process. The exposed silicon is etched to release the structure. In step (e), the exposed silicon is

etched to a specific depth to facilitate the release of the structure. In step (f),  $XeF_2$  gas is used to release the parylene based structures. In step (g), oxygen plasma is used to strip the photoresist.

### III. Test structure design

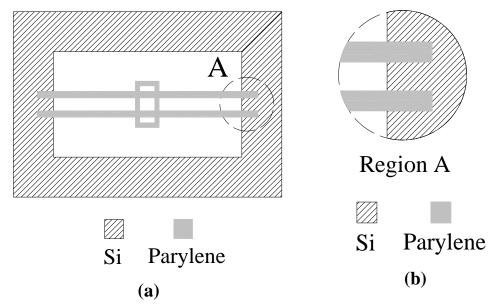

To verify the feasibility of the suspended parylene-based structure, a sample is produced, as illustrated in Figure 6 (a). Due to the poor adhesion force between the parylene and silicon [12], parylene anchors are designed to plug into the silicon to enforce adhesion, as shown in Figure 6 (b). In this manner, the parylene beams could be moved easily by applying force to the middle part of the beams. The dimensions of the parylene beams are 3000 *um* in span, 20 *um* in width, and 50 *um* in depth following fabrication.

Figure 6. (a) Layout of test device for suspended parylene structure, (b) close-up view of anchor design.

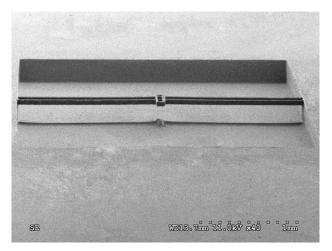

Figure 7. SEM photo of test device.

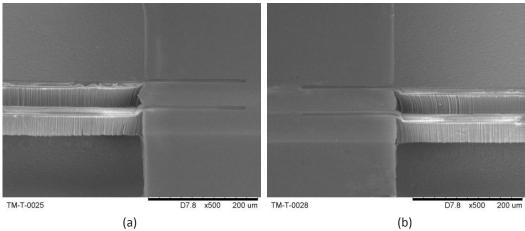

Figure 8. Close-up view of both-end sides of parylene anchors.

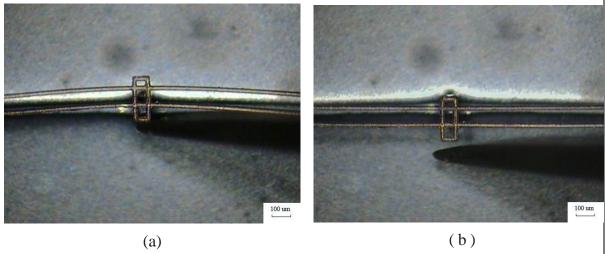

Figure 9. CCD photos of test device driven by probe tip (a) approximately 100 um of in-plane displacement, (b) releasing approximately 100 of in-plane displacement.

#### IV. Results and Measurements

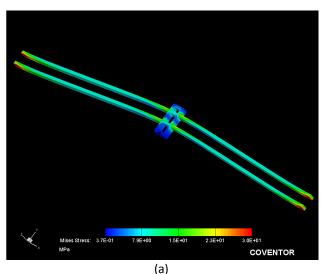

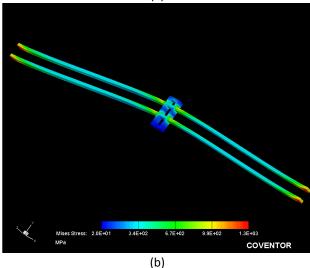

Figure 7 presents an SEM image of free-standing parylene structures, while Figures 8 (a) and 8 (b) respectively illustrate the right and left side close-up views of the parylene anchors. Figures 9 (a) and 9 (b) respectivley show CCD photos of the test device driving the tip of a probe causing 100 um of in-plane compression/release displacement. The Young's modulus of high-aspect-ratio of the parylene beam is about 4.7GPa [6], and that of single crystal silicon is about 150GPa. Compared to single crystal silicon, the parylene-based test device presents a high degree of elastic deformation. To evaluate the characteristics of ductility in the proposed devices, we simulate the maximum stress and stress distribution, and compare these values with those of silicon, the material traditionally used for MEMS. Using the same 100 um of in-plane displacement at the center of the device, Figures 10 (a) and 10 (b) respectively show the CoventorWare simulation results of stress distribution

for parylene and silicon. The maximum Von Mises stresses are generated at the anchors for both materials. The parameters used in the simulations are illustrated in Table 1. Table 2 shows that the maximum Von Mises stresses of the simulation results are lower than their yield strength. The maximum Von Mises stress of the parylene-based test devices (30MPa) is only 2.3 % of that in silicon (1.3GPa). Parylene is a high-aspect-ratio structural material, well suited to use in devices with large in-plane displacements and low stiffness.

Table 1. Material properties of parylene C and Single Crystal Silicon (100) in test device simulations

| Material                 | parylene C | Single Crystal Silicon (100) |

|--------------------------|------------|------------------------------|

| Yield Strength (MPa)     | 55 [13]    | 7000                         |

| Young's Modulus<br>(GPa) | 4.7 [6]    | 150                          |

| Poison ratio             | 0.4 [14]   | 0.17                         |

| Density ( kg / m³)       | 1289 [13]  | 2330                         |

Table 2. Maximum Von Mises stresses of simulation results generated by the same 100  $\, m$  of in-plane displacement at the center of for Single Crystal Silicon (100) and parylene test structures, respectively.

| Material                       | Parylene C | Single Crystal Silicon<br>(100) |

|--------------------------------|------------|---------------------------------|

| Maximum Von Mises stress (MPa) | 30         | 1300                            |

| Yield strength (MPa)           | 55         | 7000                            |

| Stress ratio (parylene/SCS)    |            | 2.3%                            |

Figure 10. Von Mises stress distribution of Coventorware simulation generated by 100 m of in-plane displacement at center of device for (a) parylene and (b) silicon.

#### V. Conclusion

A new process for fabricating suspended parylene-based structures is presented. The process uses a silicon micro trench as a mold, in which parylene beams are fabricated through the deposition and removal of parylene in multiple stages, after which the structure is released from the same side of the silicon

wafer. Compared to traditional processes, this approach eliminates the deposition of unnecessary silicon-dioxide, overcomes the need for double-sided micro-machining and supports the wafer during the release of the structure, thereby reducing process complexity and production costs. Without the need for thermal oxide, the process can be performed at low temperatures without wet-etching. A test device is fabricated to verify the feasibility of the suspended parylene-based structure. The dimension of the free-standing test structures are 20 um in width, 3000 um in span, and 50 um in thickness. Thanks to the ductility characteristic of the parylene beams, the devices provide elastic deformation of up to 100 um. Coventorware simulation results show that the parylene generated only 2.3% of the maximum Von Mises stress compared to the same dimensions of a silicon-based test device. This new process is well suited for use in devices with large in-plane displacement and low stiffness.

#### VI. Acknowledgement

This work is supported by the National Science Council, Taiwan, R.O.C. under award number NSC 97-2218-E-327-002. The authors would like to especially thank the NTU NEMS Research Center for simulation support.

#### References

- [1] J. W. Weigold, K. Najafi, and S. W. Pang, "Design and fabrication of submicrometer, single crystal si accelerometer," *Microelectromechanical Systems, Journal of*, vol. 10, no. 4, pp. 518-524, 2001. doi: 10.1109/84.967374

- [2] H. Luo, Z. Gang, L. R. Carley, and G. K. Fedder, "A post-cmos micromachined lateral accelerometer," *Microelectromechanical Systems, Journal of*, vol. 11, no. 3, pp. 188-195, 2002. doi: 10.1109/JMEMS.2002.1007397

- [3] Y. J. Yang, W. C. Kuo, K. C. Fan, and W. L. Lin, "A 1 × 2 optical fiber switch using a dual-thickness SOI process," *Journal of Micromechanics and Microengineering*, vol. 17, no. 5, p. 1034, 2007. doi: 10.1088/0960-1317/17/5/025

- [4] Y. J. Yang, B. T. Liao, and W. C. Kuo, "A novel 2 × 2 mems optical switch using the split cross-bar design," *Journal of Micromechanics and Microengineering*, vol. 17, no. 5, p. 875, 2007. doi: 10.1088/0960-1317/17/5/005

- [5] Y. C. Tai, "Parylene biomems," in *IEEE International Conference on Robotics and Biomimetics (ROBIO)*, 2005, pp. xxxvii.

doi: 10.1109/ROBIO.2005.246388

- [6] W. C. Kuo, C. W. Chen, and C. M. Liu, "Design and fabrication of a high-aspect-ratio parylene-based comb-drive actuator for large displacements at a low driving force," Journal of Micromechanics and Microengineering, vol. 23, no. 6, pp. 065021, 2013. doi: 10.1088/0960-1317/23/6/065021

- J. Lee, H. Shin, S. Kim, S. Hong, J. Chung, H. Park, and J. Moon, "Fabrication of atomic force microscope probe with low spring constant using SU-8 photoresist," Japanese Journal of Applied Physics, vol. 42, pp. L1171-L1174, 2003. doi: 10.1143/JJAP.42.L1171

- V. Kale and T. Riley, "A production parylene coating process for hybrid microcircuits," IEEE Transactions on Parts, Hybrids, and Packaging, vol. 13, no. 3, pp. 273-279, 1977. doi: 10.1109/TPHP.1977.1135214

- Y. Suzuki and Y. C. Tai, "Micromachined [9] high-aspect-ratio parylene spring application to low-frequency accelerometers," Journal of Microelectromechanical Systems, vol. 15, no. 5, pp. 1364-1370, 2006.

doi: 10.1109/JMEMS.2006.879706

- Laermer and A. Schilp, "Method of anisotropically etching silicon," US Patent 5501893,

- [11] A. A. Ayón, R. Braff, C. C. Lin, H. H. Sawin, and M. A. Schmidt, "Characterization of a time multiplexed inductively coupled plasma etcher," Journal of Electrochemistry Society, vol. 146, no. 1, pp. 339-349, 1999. doi: 10.1149/1.1391611

- [12] H. W. Lo, W. C. Kuo, Y. J. Yang, and Y. C. Tai, "Recrystallized parylene as a mask for silicon chemical etching," in 3rd IEEE International Conference on Nano/Micro Engineered and Molecular Systems (NEMS), Sanya, China, 2008, pp. 881-884.

doi: 10.1109/NEMS.2008.4484464

- [13] G. Srl, Typical properties of galxyl® films, 2010.

- [14] T. A. Harder, T. J. Yang, Q. He, C. Y. Shih, and Y. C. Tai, "Residual stress in thin-film parylene-c," in The Fifteenth IEEE International Conference on Micro Electro Mechanical Systems (MEMS), Las Vegas, USA, 2002, pp. 435-438.

doi: 10.1109/MEMSYS.2002.984296